# FPGA Based **BiSS C Splitter**

Austin Gnecco<sup>1</sup>, Tyler Johnson<sup>2+</sup>

<sup>1</sup>LCLS Intern 2020

<sup>2</sup>Linac Coherent Light Source, SLAC National Accelerator Laboratory, 2575 Sand Hill Road, Menlo Park, CA 94025, USA.

NATIONAL

ACCELERATOR

LABORATORY

\*Contact: tjohnson@slac.stanford.edu

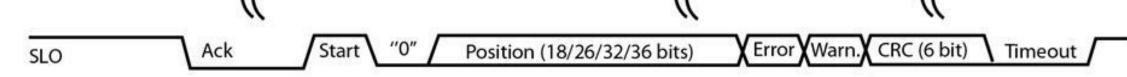

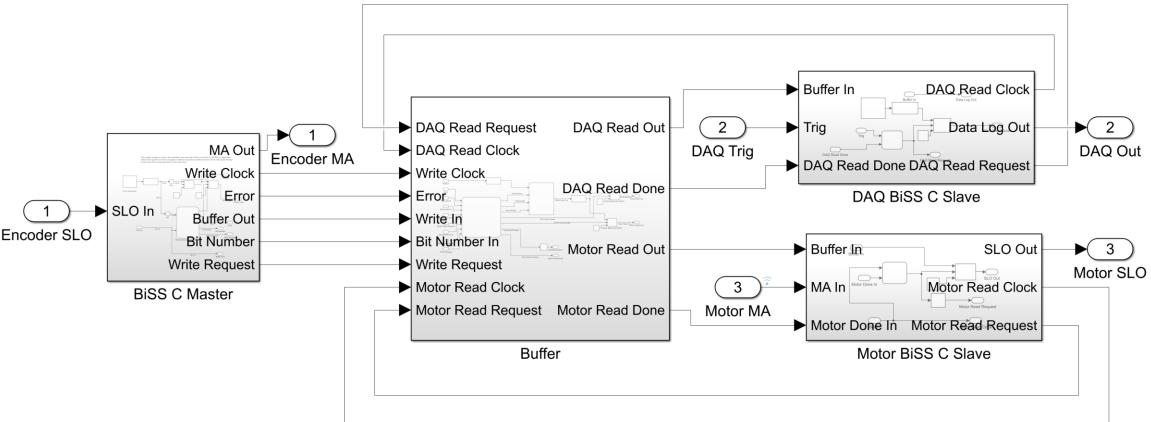

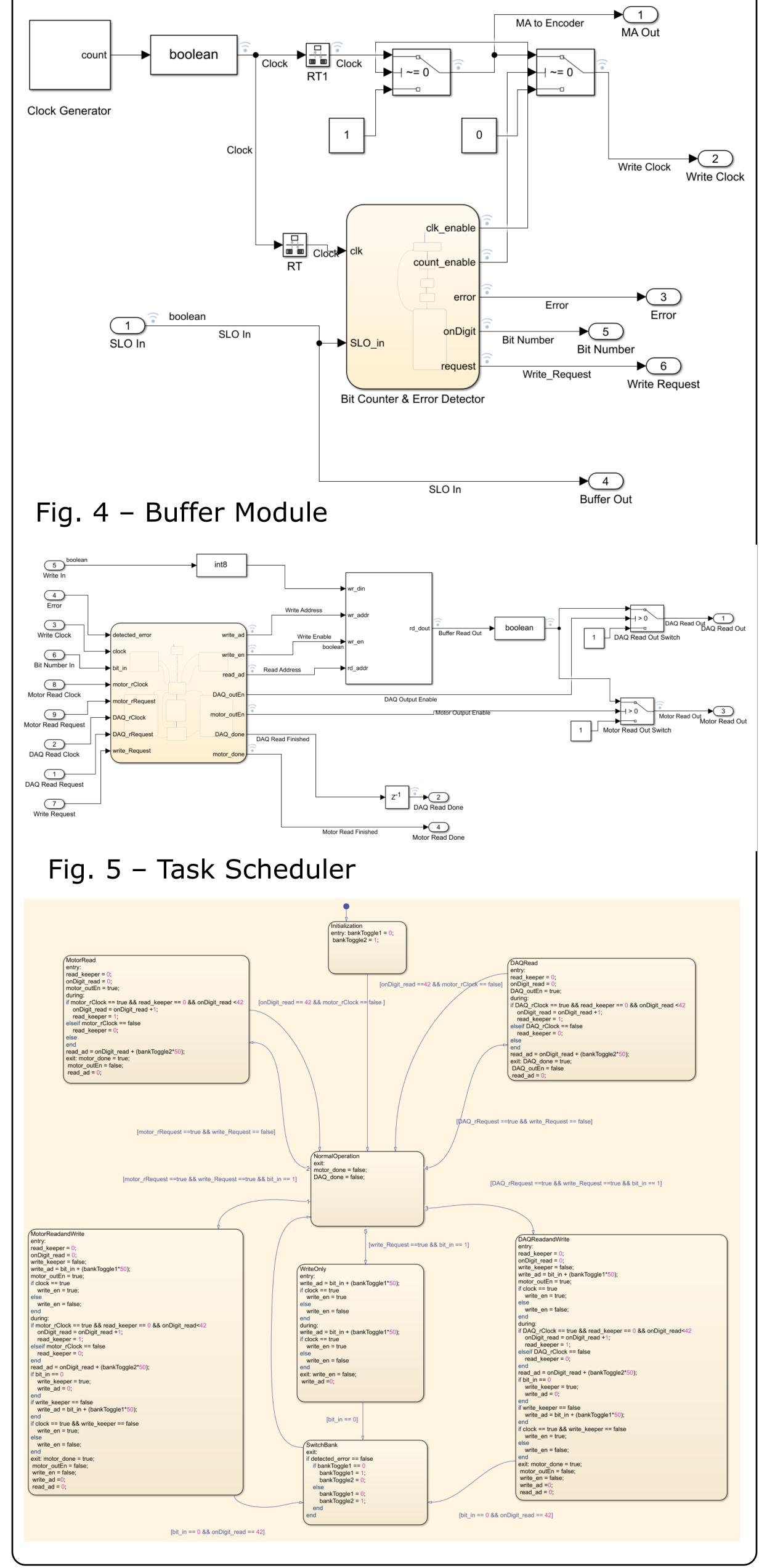

**MATLAB** Design **Design Continued** Introduction Fig.1 – BiSS C Waveform The problem that I was tasked with C Slave modules (on the right of Fig. 2) to find a way to record the process requests from the DAQ and was  $\mathbb{A} \times \mathbb{A} \times$ information from a closed loop encoder motor by signaling the Task Scheduler system, so that it could be monitored by when either requests new encoder Error Warn. CRC (6 bit) Timeout Position (18/26/32/36 bits) Start "0" the greater LCLS beamline control location data. system. Currently, there are extremely To reduce latency, read requests precise encoders on the LCLS mirror from the motor have the highest priority Fig. 2 – System Overview tables, however, they only communicate and will be executed first. If there is also with their attached motor, and do not a request to write new information from offer a native option to record position DAQ Read Clock the encoder at the same time as a DAQ Read Out ▶(2) data. request to read information, the two **DAQ** Trig DAQ Read Clock DAQ Out Encoder M DAQ Read Done DAQ Read Regu Write Clock Write Clock The proposed solution was to design DAQ Read Done can happen simultaneously events DAQ BiSS C Slave (1) SLO In Buffer Out Write In Encoder SLO a FPGA based signal splitter to be used Bit Numbe Bit Number In through the dual bank design: When new → 3 Motor Read Out SLO Out Buffer In Write Reques Motor SLO with the encoders on the mirror tables at Motor Read Clock (3) **BiSS C Master** information from the encoder is received, Motor Read Done Motor MA Motor Done In Motor Read Reque LCLS. The job of this signal splitter is to it is written to bank 1. While new data is Motor BiSS C Slave take the position information from the being written, the old data can be read encoder and (upon request) deliver that off bank 2, to either the motor or the Fig. 3 – BiSS C Master Module information to either the control motor or DAQ. Assuming that no errors are →<u>1</u> MA Out MA to Encoder a data acquisition device to log its detected, the banks switch, making bank boolean position or report it to the greater control Clock 2 the most recent data that is sent out of ▶⊣ ~= 0` \_\_\_\_ system. the device, while bank 1 is written over **Clock Generator** I approached this design by first with new information from the encoder. If 0 creating a simulation in MATLAB, and Clock ▶ 2 an error is detected, the banks do not Write Clock Write Clock then using that simulation to generate switch, and the corrupt data is written the VHDL code that will be used to run over by new data before it is read. clk\_enable the splitter. The VHDL code will then be Although this structure is not without count enable applied to a Artix-7 development board, flaws (most noticeably, two reads ▶ 3 error Error to split the signals. cannot happen at once and when a write boolean ▶ 5 onDigit SLO In Bit Number SLO In has started, a read must wait until the Bit Number ▶ 6 reques Write Request write finishes to begin) structure helps to Write Request Bit Counter & Error Detector minimize latency, while being as accurate Design as possible and still allowing for the Many potential designs were created, encoder, motor, and DAQ to all read and ► 4 Buffer Out SLO In write data at their native clock speeds. but eventually the one that was settled Fig. 4 – Buffer Module

on used two banks of memory that would be switched between to provide the most accurate position information. The design works as such:

The encoder and motor use a protocol called BiSS-C in order to communicate (Fig. 1). In this protocol, a signal is sent on the MA line from the commanding device to act as a clock. It a square wave that can range 10mhz anywhere between 1mhz and depending on the device. As not every device is required to use the same frequency, the splitter had to be capable of dealing with multiple clock speeds at the same time. All interactions with the encoder are controlled through the BiSS-C Master Module(Fig. 3). This module continuously sends a 10 MHz square wave to the encoder, in order to request new location as possible. As often the data as information is received back from the encoder, this module also counts the number of bits received and looks for errors before passing the information on to the buffer module. Upon the encoder signals entering the Buffer Module (Fig. 4), the Task Scheduler (Fig. 5) looks at all of the different signals coming into the FPGA decides which requests will be and executed first. The DAQ and Motor BiSS

## Conclusions

Although the final implementation of code is ongoing, the MATLAB this simulations have shown that this splitter design is capable of quickly and accurately storing data to be shared between two different devices.

This design will be further validated through simulation of the generated VHDL code using Vivado before it will be tested on the actual encoder, motor and DAQ hardware at LCLS. The ability for LCLS operators to log and verify the positions of mirrors on the beamline should allow for a more complete view of beamline devices.

### Acknowledgments

Use of the Linac Coherent Light Source (LCLS), SLAC National Accelerator Laboratory, is supported by the U.S. Department of Energy, Office of Science, Office of Basic Energy Sciences under DE-AC02-76SF00515. No. Contract Additionally, this project would not have been possible without the support of my mentor Tyler Johnson.

Date: 9/10/2020